内容简介

芯片在我们日常生活中无处不在。近年来,物联网、人工智能的兴起,也带来了加速器和边缘计算芯片设计的热潮。然而,芯片虽小,其制造过程却极其复杂。一般而言,制造过程需要经历反复的光刻、气相积淀、研磨等步骤才能在晶圆(Wafer)上形成电路。如果芯片设计与制造工艺不匹配或者制造过程出现偏差,将会导致晶圆上出现缺陷,轻则影响电路性能,重则导致短路、开路等功能障碍 。因此,芯片设计需要在制造前通过工艺模型反复仿真验证,确保大规模生产的良率。目前高精度工艺模型往往需要物理级别仿真(如Synopsys Sentaurus Lithography等工具),计算复杂度高,在整体芯片(Full Chip)验证中遇到较大算力方面的挑战。

北京大学高能效计算与应用中心助理教授林亦波与美国德克萨斯大学奥斯汀分校David Pan教授团队及日本Kioxia(原东芝存储)半导体公司合作,利用深度对抗学习,对制造流程中的关键光刻系统进行建模,在工业级精度范围内,较物理级别仿真实现了1000倍以上的加速。相关工作获得了2020年ACM国际物理设计专题研讨会(ISPD)的最佳论文奖。

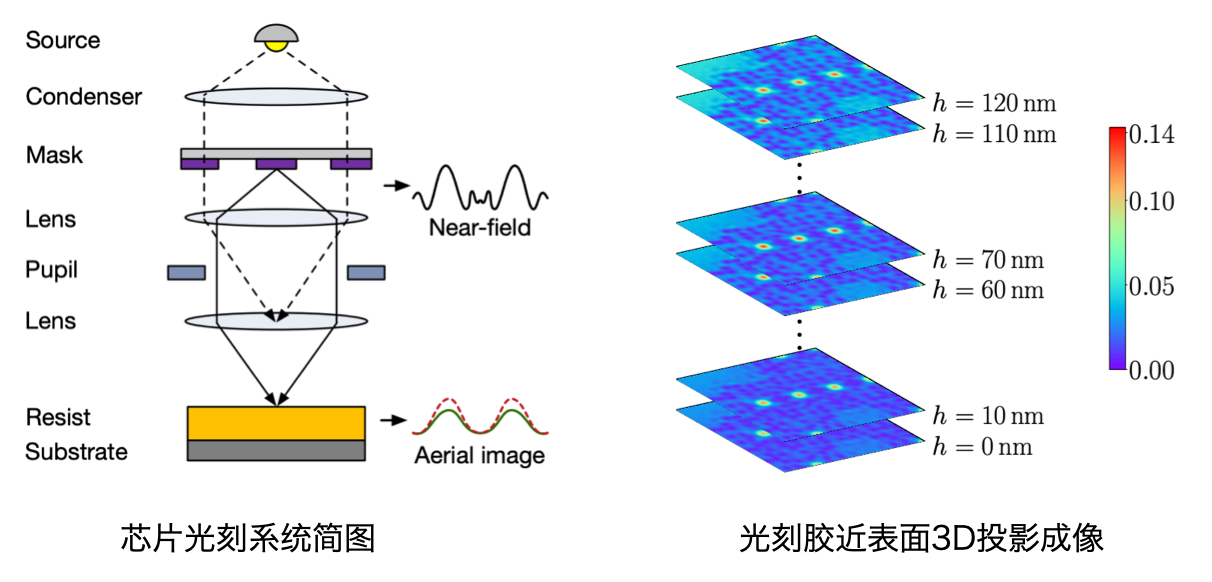

以下为论文内容概要。在芯片光刻系统中,芯片设计起到掩膜(Mask)的作用(大学物理都学过双缝干涉实验吧~类似的原理)。光从光源发出,经过光学成像系统,在光刻胶(Resist)近表面形成三维空间影像(3D Aerial Image)。根据不同位置空间影像光强的大小,会在光刻胶上刻出不同的图案(Pattern)。这些图案的大小、位置决定了实际电路的电容电阻等电气指标,最终影响芯片的性能。而对光刻胶近表面三维空间影像的预测是精确计算刻蚀图案的关键。

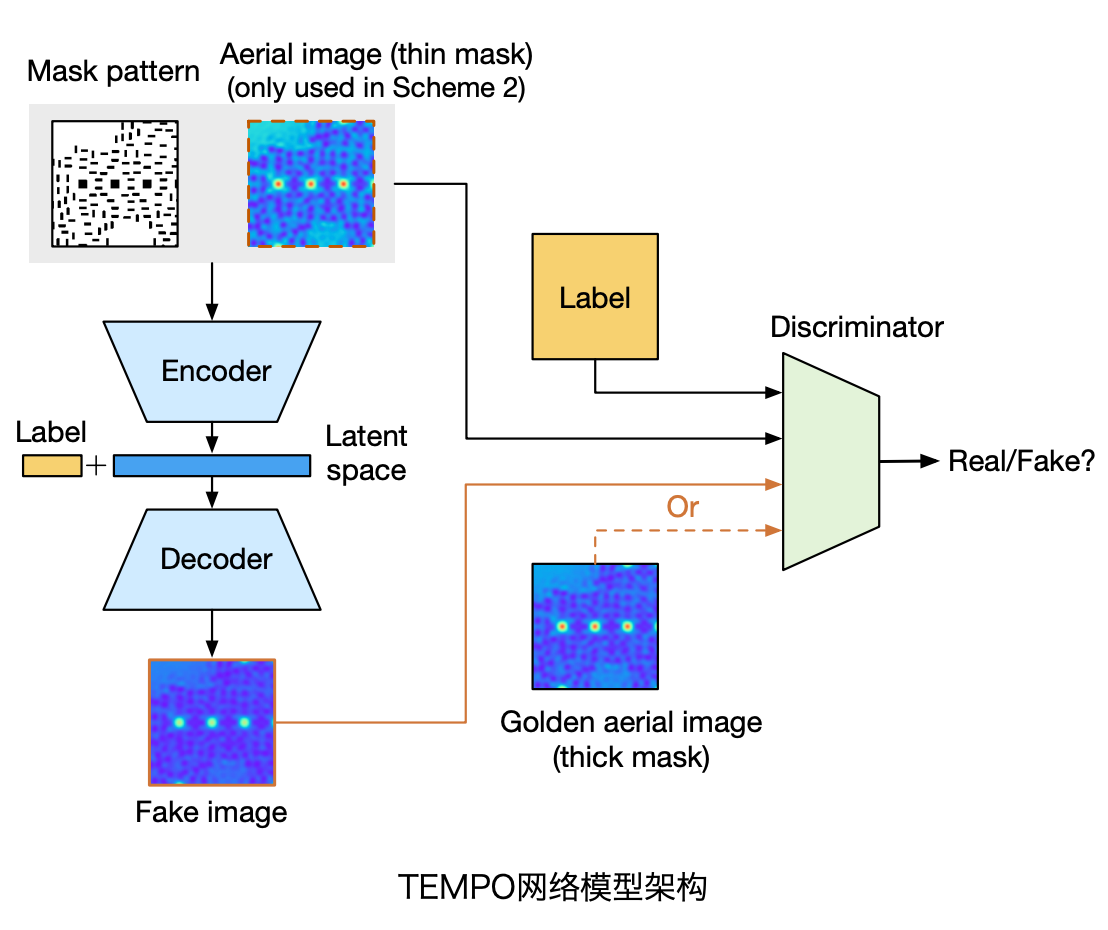

论文提出了从二维掩膜设计转译到三维空间影像的深度对抗学习框架TEMPO (Fast Mask Topography Effect Modeling with Deep Learning)。该方法首先将三维空间影像二维化,通过等间距切割形成一组代表不同层级的二维空间影像;再利用在Latent Space注入层级标签的方式,选择预测哪一层的影像;最后将每一层结果拼接起来得到最终的三维空间影像。TEMPO采用对抗生成网络StarGAN作为基础网络架构,并针对该问题的特殊性提出了一系列优化方案。最终在工业级的数据集上,实现了1nm以内的平均误差和1170倍加速。另外,为了进一步提高预测精度,论文将传统方法与深度学习方法结合,抽取物理级别仿真的快速中间结果,辅助模型预测,能够将平均误差降低至0.5nm以内,并仍然实现了27倍的计算总效率提升。更多详情请关注论文:https://doi.org/10.1145/3372780.3375565

部分作者信息

叶葳,Facebook研究科学家(Research Scientist)。2015年于浙江大学电气工程学院获得工学学士学位,2020年于美国德克萨斯大学奥斯汀分校电子与计算机工程系获得博士学位。2020年6月加入Facebook On-Device AI group。她的研究兴趣包括高能效边缘AI计算和基于机器学习的芯片设计自动化。个人主页:https://ywwwer.github.io/publications/

林亦波,北京大学高能效计算与应用中心助理教授。2013年毕业于上海交通大学微电子系,获得理学学士学位。此后分别于2017年和2018年在美国德克萨斯大学奥斯汀分校电子与计算机工程系获得硕士和博士学位。2019年6月加入北京大学信息科学技术学院。他曾获2019年设计自动化大会(DAC)、2018年Integration期刊、2016年SPIE Advanced Lithography会议的最佳论文奖。他目前的研究兴趣包括基于机器学习的芯片设计自动化(EDA)算法以及GPU/FPGA加速。个人主页:http://yibolin.com.cn/

David Z. Pan is Engineering Foundation Professor at the Department of Electrical and Computer Engineering, University of Texas at Austin. His current research focuses on synergistic AI and IC design and automation. He has published over 375 refereed journal/conference papers and 8 US patents. He has served in many journal editorial boards and conference committees, including various leadership roles. He has received many awards, including SRC Technical Excellence Award in 2013, 19 Best Paper Awards at premier forums, DAC Top 10 Author Award in Fifth Decade, ASPDAC Frequently Cited Author Award, Communications of ACM Research Highlights, ACM/SIGDA Outstanding New Faculty Award, NSF CAREER Award, IBM Faculty Award (4 times), UCLA Engineering Distinguished Young Alumnus Award, UT Austin RAISE Faculty Excellence Award, Cadence Academic Collaboration Award, and many international CAD contest awards. He has graduated 32 PhD students who are holding key academic and industry positions, and have won many awards including the First Place of ACM Student Research Competition Grand Finals in 2018, ACM Outstanding PhD Dissertation in EDA Award (twice), EDAA Outstanding Dissertation Award (twice), and so on. He is a Fellow of IEEE and SPIE.

Webpage: http://users.ece.utexas.edu/~dpan/